See this post for information about NCL signals.

Symbol

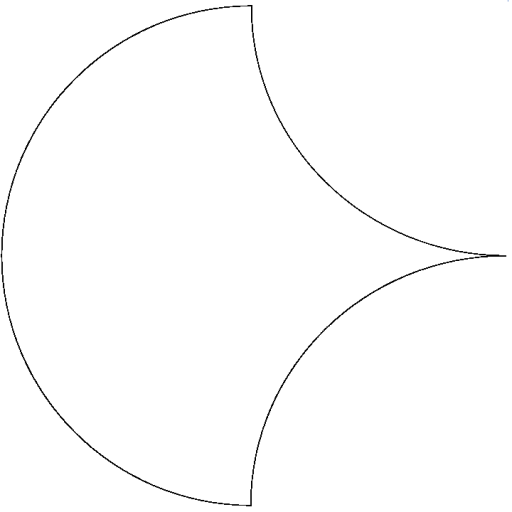

It may or may not surprise you to know that NCL has it’s own set of gates for building circuits. They are called threshold gates and are drawn as

with the ‘threshold number’ in the middle. The inputs come in on the left (round) part, and the output comes out the point on the right.

Operation

For all threshold gates:

- If all inputs are 0, the output is 0

- If the number of inputs that are set is >= the threshold number, the output is 1

- Otherwise, it holds its value.

threshold gates can have input weights, meaning that an input can count towards the threshold count more than once.

Notation

A threshold gate is denoted as THmn where m is the threshold value (the number of inputs needed to transition to a 1) and n is the total number of inputs. If weights are needed, then THmnW## is used, where the #’s are replaced with the weights (order is irrelevant). A TH23W2 gate sets when the first input is set (as it is counted twice), or when both of the other 2 are set. The boolean logic function is

TH23W2 Set: A+BC

Note that when just B or C are set, the gate keeps its value, so if it was a 1, then it will stay a 1, and if it was a 0 it will stay a 0. The logic function for clearing the gates is essentially the same for all:

THm1 Clear: A' THm2 Clear: A'B' THm3 Clear: A'B'C' THm4 Clear: A'B'C'D

Summary

Threshold gates are used in NCL because they are less volatile than standard gates. Once they have an output, they hold on to int until their inputs are completely cleared (circuit reset). This means that a NCL component’s output will not flip more than once in an operation. This property of threshold gates means that if the outputs are set, the component has completed, and if they are reset, it has cleared. You always know when it is ready to move on.