The THxor0 Gate is a 4-input gate with logic function AB + CD. Data that I have found about implementing this gate is all at the transistor level. For now, I’ll make a behavioral model, but I may later design a structural version (technically a 1-bit state machine). Regardless, I think this implementation is actually synthesizable, so that’s nice

The behavioral implementation:

entity THxor0 is

generic(Delay : time := 1 ns);

port(A, B, C, D : in std_logic;

output : out std_logic);

end THxor0;

architecture behavioral of THxor0 is

begin

process (A, B, C, D)

begin

if (A = '0' and B = '0' and C = '0' and D = '0') then

output <= '0';

elsif ((A and B) or (C and D)) = '1' then

output <= '1';

end if;

end process;

end behavioral;

The process statement again has 2 conditions: Set and Clear. If neither is met, the gate holds it’s state.

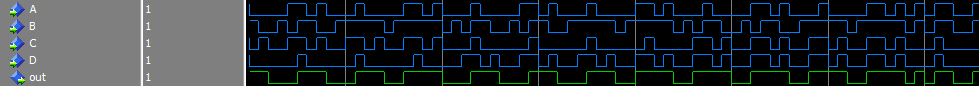

Testing

The test script was a modified version of the THmn test script. See scripts/test/test_threshold_gate.tcl on GitHub. Below is an excerpt from the test simulation session.

See this post for a Half Adder component that uses this gate.

Commit: 19c8318

One Reply to “NCL THxor0 Gate”