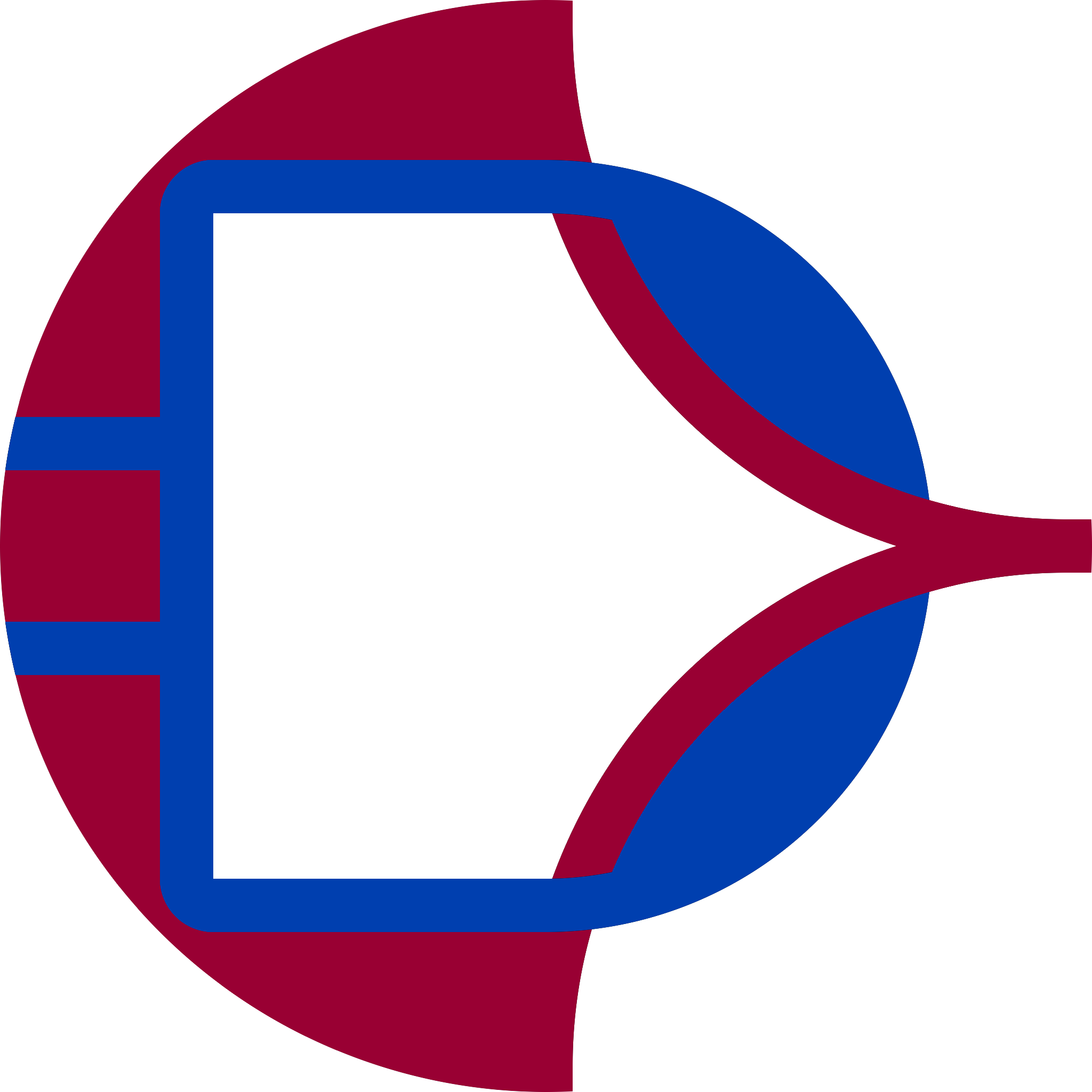

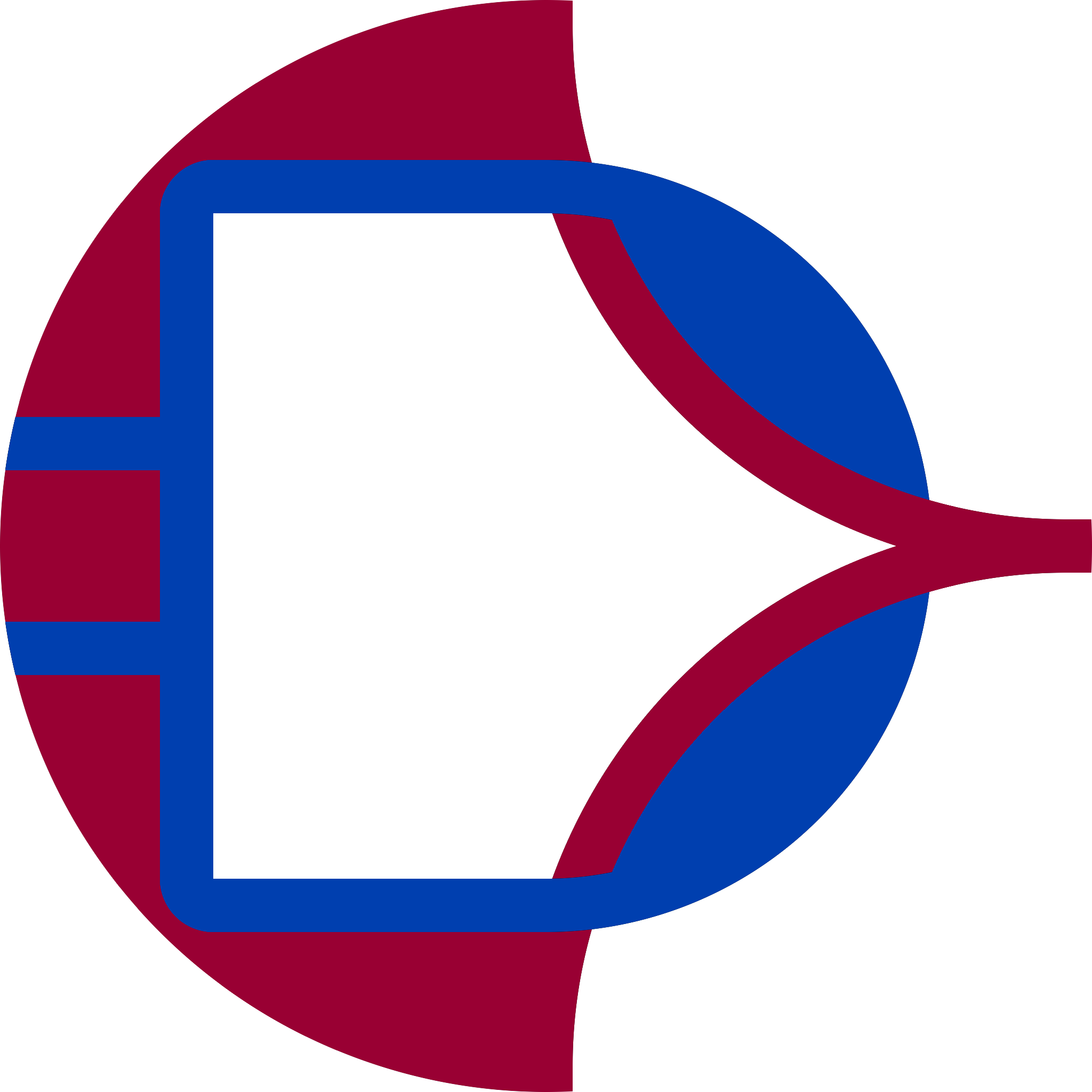

I want to explain the logo a bit:

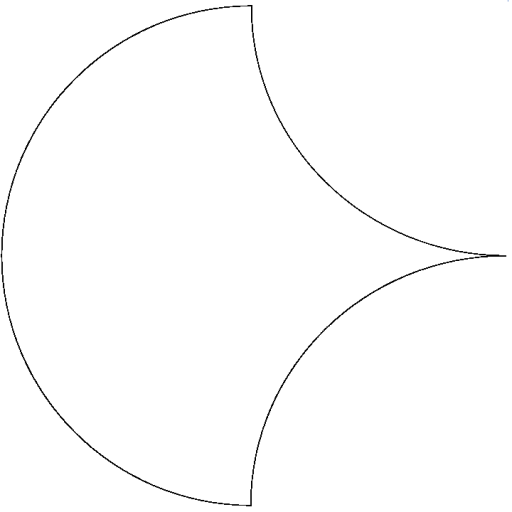

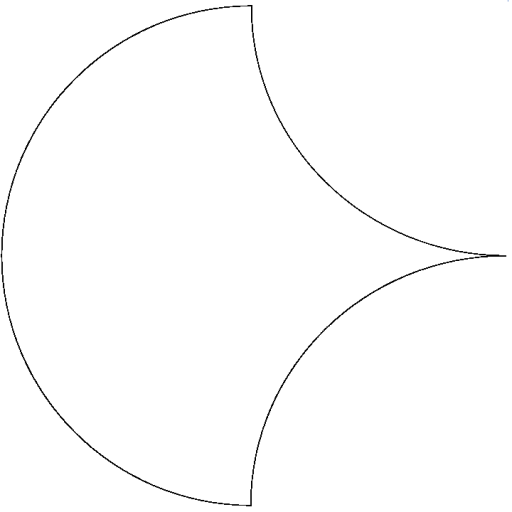

It’s three relevant logic gates in one. The red portion is a Threshold Gate:

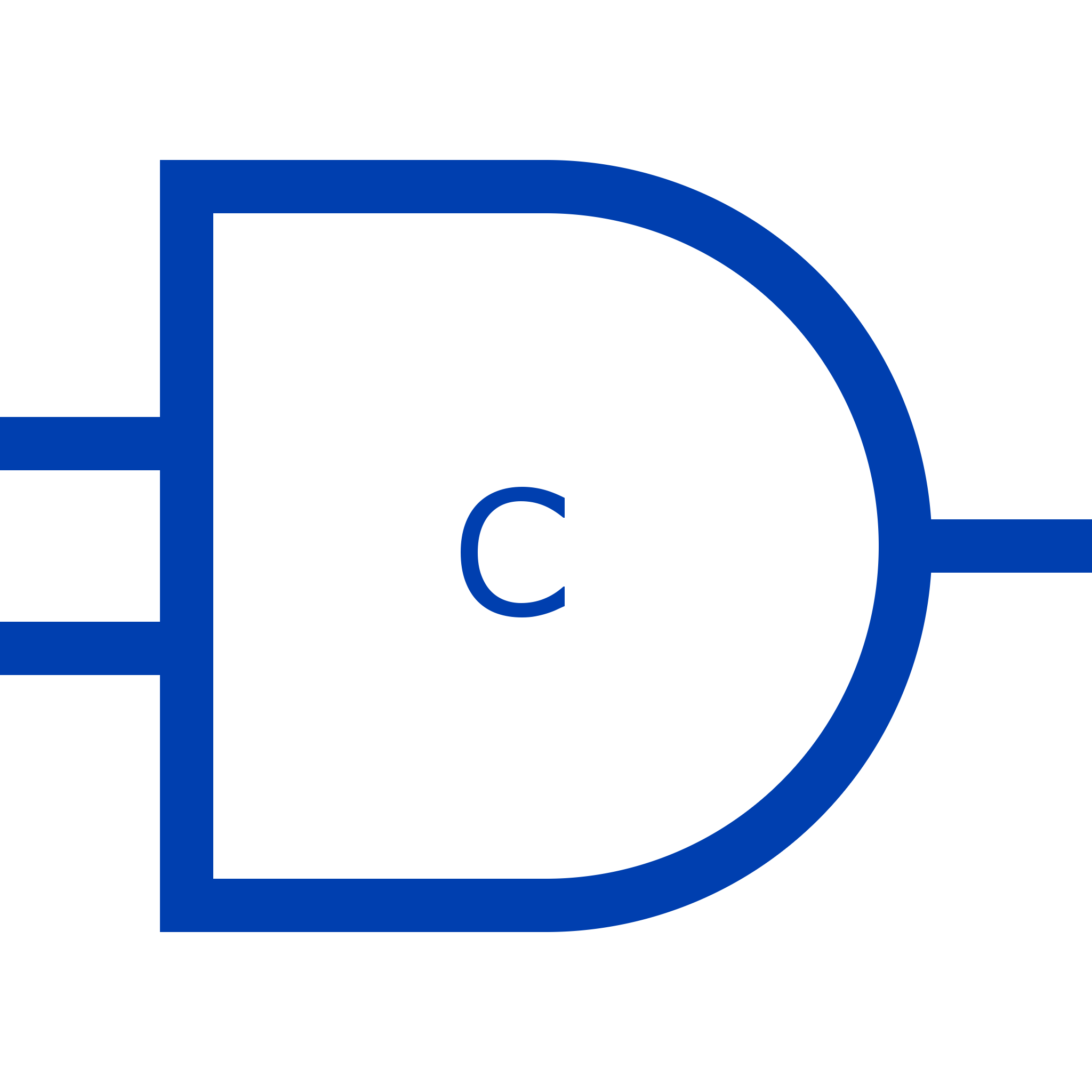

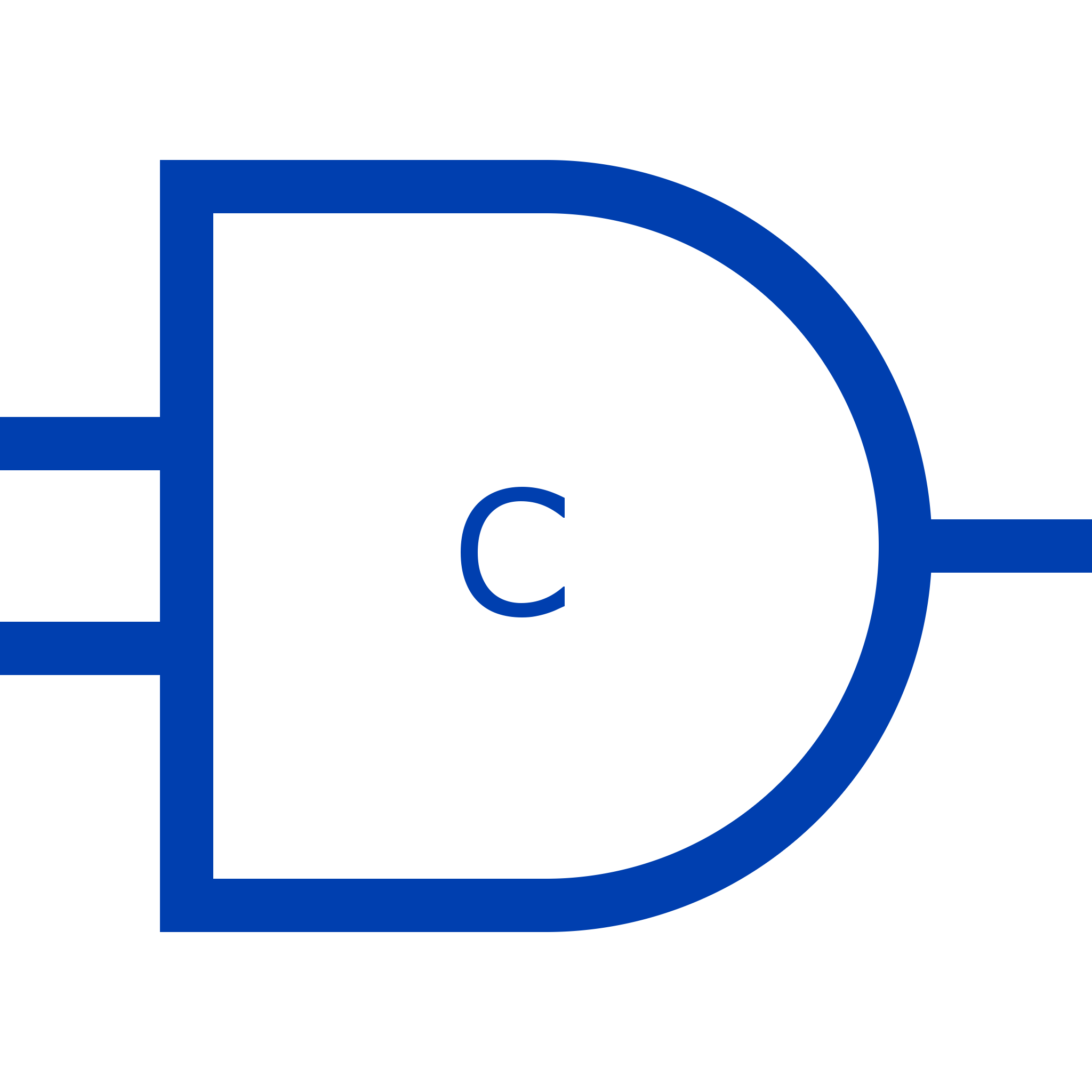

Threshold gates are used by NCL logic. The next gate is the blue one, you may recognize it as an AND gate. Some models of Asynchronous Logic use something called a C-Element, which is drawn like an AND-gate, but it has a ‘C’ in the middle (not shown in the logo). C-Elements are functionally identical to a TH22 gate.

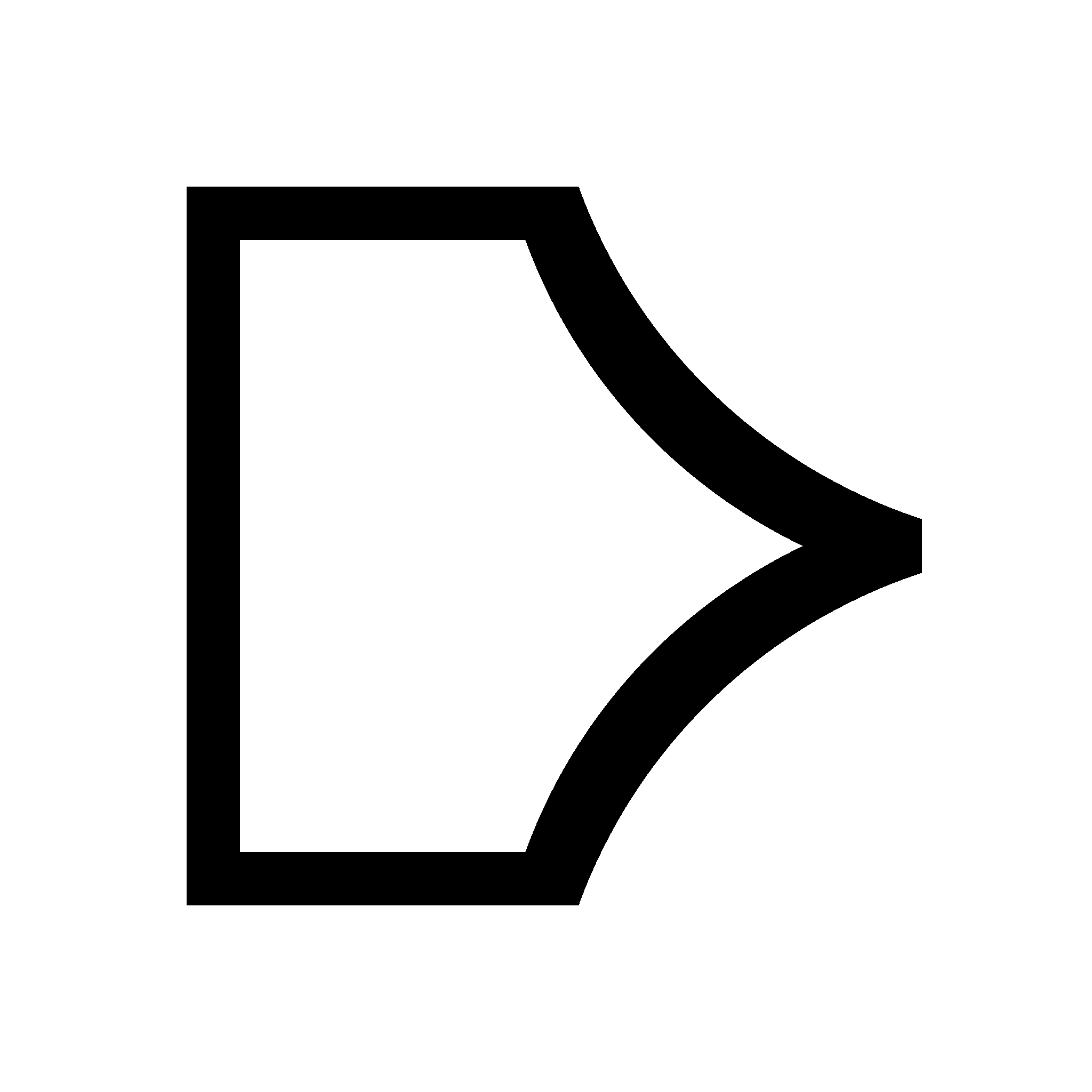

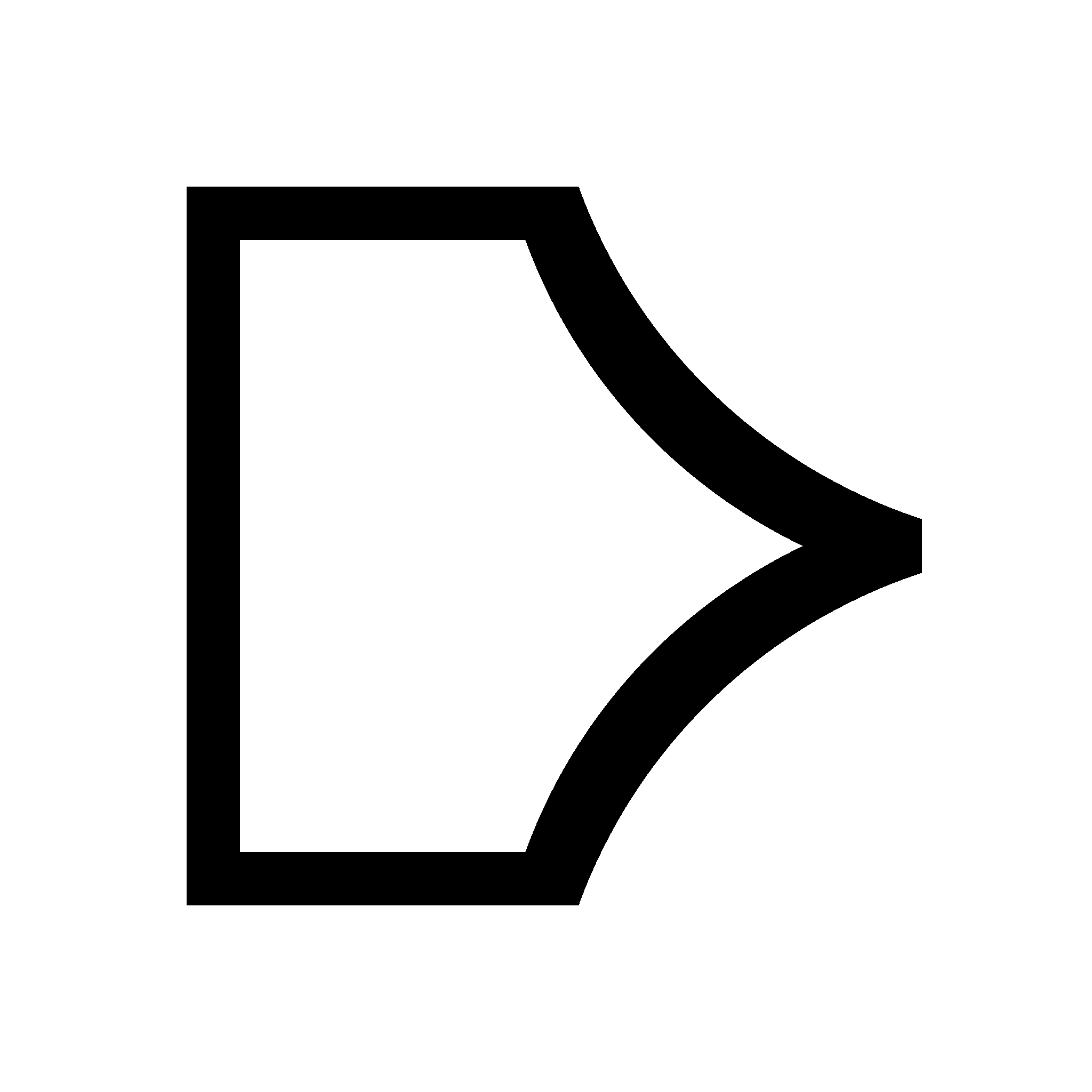

The white portion in the middle was not actually something I planned, but I was quite pleased when I noticed the shape. It is the shape of an NCL Threshold gate without hysteresis. These gates aren’t (to my knowledge) used directly very often in designs, but they are the blocks that Threshold Gates with hysteresis are built on.

This is done by feeding the output back to the input m-1 times on an (n+m-1)-input non-hysteresis gate with the same m (see this post).

And of course I tried to make it all look sorta cool. Though I admit, it might be too complex for the 16×16 browser tab icon.

If you want, I can provide the GIMP project on GitHub. If you have suggestions for improvements, let me know.